# Review paper

## **Voltage Mode Drivers for Serial-Link Applications: Review**

Aboubakr Elsayed Mohamed<sup>1</sup>, Sameh A. Ibrahim<sup>2</sup>, El-Sayed Hasaneen<sup>1,\*</sup>, and Ahmed M. Mohamed<sup>1</sup>

<sup>1</sup> Department of Electrical Engineering, Aswan University, Aswan, Egypt

#### Abstract

Serial links have emerged as a pivotal and widely adopted solution for enabling high-speed data communication among various devices and components in modern electronic systems, serving critical roles across diverse applications, including networking, computing, and data storage. Their increasing popularity can be attributed to their ability to facilitate efficient and reliable data transfer, which is essential for the optimal performance of increasingly complex electronic environments characterized by the need for rapid data exchange and real-time processing. However, the design and implementation of effective serial links present a myriad of significant challenges that engineers must adeptly navigate. Achieving high data rates is often accompanied by the pressing need to maintain low power consumption, a crucial factor in mobile and embedded systems where energy efficiency is paramount. Additionally, ensuring robust signal integrity is vital, as even minor deviations in voltage levels or timing can lead to substantial errors in data transmission, which can critically impact system performance and reliability. This article aims to explore the various innovative techniques proposed for voltage mode (VM) transmitters specifically tailored for serial-link applications. By thoroughly examining the strengths and limitations of these techniques, we seek to shed light on the cutting-edge approaches that not only enhance performance but also effectively address the inherent design challenges. Our goal is to contribute to the advancement and development of high-performance se- rial communication systems that meet the demanding requirements of today's technology landscape, ensuring that they can support the ever-increasing data rates and complexity of modern applications while maintaining the necessary reliability and efficiency. Through this exploration, we aim to provide insights that will be valuable to engineers and researchers working in the field, facilitating the ongoing evolution of serial communication technology and its applications.

Keywords: VM; CM; NRZ; PAM-4; RLM.

#### 1 Introduction

Integrated circuit (IC) design is fundamental to a wide range of sectors, including consumer electronics, computing, telecommunications, automotive systems, medical devices [1], and industrial automation. These circuits serve as the backbone of modern technology, enabling the functionality of essential devices such as smartphones, computers, and various household appliances. Moreover, ICs are critical in emerging fields like the Internet of Things (IoT), aerospace, power management, and embedded systems, where they facilitate seamless communication and control among inter- connected components.

<sup>&</sup>lt;sup>2</sup> Department of Electronics and Communications Engineering, Ain Shams University, Cairo, Egypt

One of the most prevalent solutions for high-speed data communication between devices is the use of serial links. These links have become a widely accepted solution for high-speed data communication among various devices and components. However, designing effective serial links presents significant challenges, as they must achieve high data rates while ensuring low power consumption and maintaining signal integrity. Although these links occupy less board space and chip perimeter, their engineering complexity, can introduce considerable risks to the first-pass success of ASICs [2]. One promising technique that has emerged to tackle these challenges is pulse amplitude modulation with four levels (PAM-4). By encoding two bits of information per symbol, PAM-4 effectively doubles the achievable data rate compared to traditional non-return-to-zero (NRZ) schemes. Nonetheless, the implementation of PAM-4 transmitters and receivers is inherently more complex and power-hungry than their NRZ counterparts. This trade-off between enhanced data rates and increased system complexity and power consumption is a critical factor to consider when designing and deploying serial-link communication systems.

PAM-4 signaling, which allows for the transmission of 2 bits per symbol, presents significant advantages for achieving higher data rates [3-5]. This is primarily because the clock frequency required for PAM-4 is only half that of NRZ signaling when transmitting the same data rate [6]. This characteristic makes PAM-4 particularly attractive in applications where bandwidth efficiency is critical. However, the PAM-4 signaling method also introduces challenges. One notable drawback is that PAM-4 signals have only one-third the eye height of NRZ signals. This reduced eye height results in a significant attenuation of signal-to-noise ratio (SNR) by approximately 9.5 dB [7, 8], which can adversely affect the reliability of data transmission. The diminished eye height makes PAM-4 signals more susceptible to noise and other distortions, which can complicate signal detection and integrity. Moreover, the non-linear characteristics of the transmitter output can lead to further SNR degradation [6]. This non-linearity may create imbalances between the various PAM-4 signal levels, resulting in inconsistencies that can impair the quality of the transmitted data. Since the overall performance of the system hinges on the smallest eye height produced by the transmitter, addressing these challenges is crucial. To optimize performance, it is essential to equalize the voltage differences between the PAM-4 signal levels [6]. This equalization helps to ensure that the levels are balanced, thereby improving the reliability of signal detection. Additionally, matching the channel impedance at each signal level is vital for minimizing reflections and maximizing signal integrity. By carefully managing these factors, designers can enhance the overall effectiveness of PAM-4 signaling in high-speed data communication systems.

Recently voltage mode (VM) drivers have become preferred over current mode (CM) drivers due to their lower power consumption. However, designing VM drivers presents several challenges for three primary reasons. First, the output swing is managed by varying the supply voltage of the driver, which requires effective supply regulation [9, 10]. Second, output impedance matching is influenced by the sizes of the devices and their terminal voltages, both of which are impacted by the output swing [10, 11]. Finally, incorporating de-emphasis can alter the terminal voltages of the output transistors, leading to degradation in impedance matching [10].

This review aims to provide a comprehensive literature review on the design of VM drivers for serial-link applications. We begin by highlighting the significance of serial links, which offer advantages such as high data rates, low power consumption, and improved signal integrity

compared to traditional parallel bus architectures. However, the design of effective serial links presents various challenges, including the need to achieve increasing data rates while ensuring robust signal integrity and low power usage. To address these challenges, we explore emerging techniques, particularly the adoption of PAM-4, which allows for the doubling of achievable data rates compared to conventional NRZ signaling. The structure of this review article is as follows: Section 2 covers the basic principles; Section 3 discusses NRZ and PAM-4 signaling; Section 4 presents the current state of VM drivers; Section 5 addresses the limitations; and Section 6 concludes the discussion.

#### **2 BASIC PRINCIPLES**

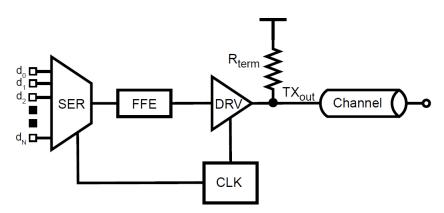

In the realm of high-speed data transmission and signal processing, driver circuits play a crucial role in ensuring reliable communication between components. A wireline transmitter (TX) performs three essential functions <a href="Fig.1">Fig.1</a>: it converts multiple parallel, low-speed data streams into a single high-speed output through serialization, employs equalization techniques to mitigate signal degradation encountered during transmission, and ensures adequate output swings for accurate interpretation by the receiver. To facilitate these operations, various clock frequencies and phases are generated using a phase-locked loop (PLL), which synchronizes the timing of the transmitted signals. Additionally, the output transistors are safeguarded by electrostatic discharge (ESD) devices, which protect against voltage spikes and enhance the overall reliability and durability of the transmitter.

Two predominant types of drivers are used in a TX circuit are CM drivers [12–17] and VM drivers [18–25]. Each type offers distinct advantages and challenges that make them suitable for different operational scenarios.

Figure 1: Generic wireline transmitter

### 2.1 Basic CM Drivers

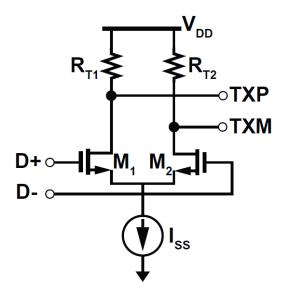

CM drivers Fig.2 operate by controlling the output current rather than the output voltage. This approach allows for faster response times and improved signal integrity, particularly in high-frequency applications [26]. By focusing on current, these drivers can effectively handle variations in load conditions, making them ideal for environments where impedance may fluctuate. However, CM drivers often require more complex circuitry and can consume more power, especially at higher data rates. Their performance is also sensitive to temperature variations and other external factors [27], which can introduce noise and degrade signal quality.

Figure 2: Basic CM driver circuit

### 2.2 Basic VM Drivers

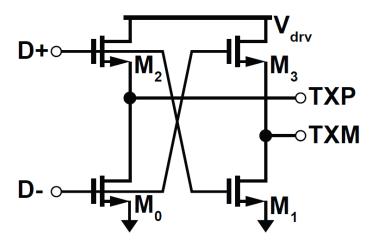

In contrast, VM drivers Fig.3 control the output voltage levels directly. This method simplifies the design and implementation of the driver circuit, leading to reduced complexity and potentially lower power consumption. VM drivers are particularly advantageous for applications where consistent output swing is essential [10]. They are widely used in systems that prioritize energy efficiency and are increasingly favored in modern designs. However, one of the challenges with VM drivers is maintaining output impedance matching [28], particularly as the output swing varies. This requires careful design considerations to ensure stable performance across various operating conditions.

Figure 3: Basic VM driver circuit

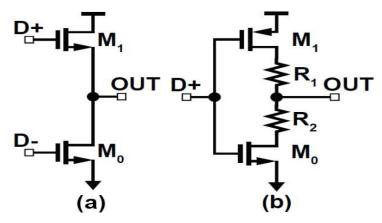

VM drivers can be categorized into two primary configurations [10]: N-over-N Fig.4(a) and P-over-N Fig.4(b) drivers, each with distinct operational characteristics and advantages. N-over-N VM Drivers utilize n-channel transistors for both the pull-up and pull-down functions. This design is particularly advantageous in low-voltage applications, where n-channel transistors generally offer better electron mobility compared to their p-channel counterparts. As a result, N- over-N drivers provide high drive capability, enabling fast switching speeds and strong output swings, which are critical for driving capacitive loads effectively. Their efficiency in handling rapid transitions makes

them suitable for modern high-speed interfaces, such as those found in data centers, telecommunications, and high-performance computing systems. Additionally, N-over-N configurations often exhibit lower power consumption during switching, contributing to overall system efficiency. In contrast, P-over-N VM Drivers employ a combination of p-channel transistors for pull-up functions and n-channel transistors for pull-down functions. This configuration facilitates effective level shifting, which is

Actually, beneficial in applications where higher output voltage levels are necessary. P-over-N drivers are designed to deliver improved voltage swings, making them ideal for systems that require robust signal levels to ensure reliable data interpretation. These drivers are commonly used in battery-operated devices and low-power applications, where energy efficiency is paramount. Their ability to maintain signal integrity in varying load conditions further enhances their utility in diverse electronic designs. Both N-over-N and P-over-N VM drivers are integral to modern communication systems, ensuring reliable data transmission across various platforms. The choice between these configurations depends on specific application requirements, including factors such as power consumption, drive strength, switching speed, and overall signal integrity. Understanding the unique characteristics and benefits of each driver type is essential for engineers and designers aiming to optimize performance in high-speed digital circuits.

Figure 4: Schematics for (a) N-over-N and (b) P-over-N VM drivers.

### 3 NRZ AND PAM-4 SIGNALING

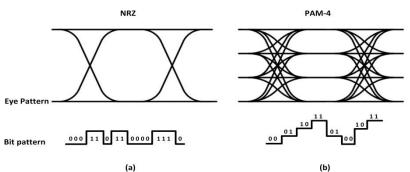

NRZ <u>Fig.5(a)</u> and PAM-4 <u>Fig.5(b)</u> are two prominent encoding schemes utilized in communication systems for the representation and transmission of binary data. These encoding techniques play a critical role in how information is formatted and sent over various media, impacting both bandwidth efficiency and signal integrity.

Figure 5: Eye Pattern and Bit Pattern for a) NRZ and b) PAM-4

### **3.1 NRZ**

NRZ is one of the simplest and most widely used encoding methods, where binary data is conveyed using two distinct signal levels typically one voltage for a binary '1' and another for a binary '0'. This method is efficient in terms of bandwidth usage, as it allows for a continuous signal that does not return to a baseline state between bits, hence the name "Non-Return-to-Zero' [29, 30]. The binary nature of NRZ data requires a single signal path with, in principle, no need for linearity [9]. Thus, NRZ signal swings are dictated by primarily speed and power considerations. However, while NRZ is straightforward and easy to implement, it faces challenges, particularly in maintaining synchronization and managing data integrity during long sequences of identical bits, which can lead to timing issues.

#### 3.2 PAM-4

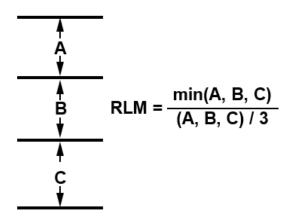

In contrast, PAM-4 is a more sophisticated encoding scheme that enhances data transmission capabilities by utilizing four distinct voltage levels to represent two bits of information per symbol. This approach effectively doubles the amount of data transmitted without requiring additional bandwidth, making PAM-4 particularly advantageous for high-speed applications, such as data centers and advanced telecommunication systems. However, the increased complexity of PAM-4 introduces challenges related to signal quality, as the closer proximity of voltage levels can make the system more susceptible to noise and other interferences. The primary issue at hand is the reduction in eye height, which can lead to an increase in the error rate of the receiver. This phenomenon is measured by the "ratio of level mismatch" (RLM) Fig.6, defined as the smallest eye height divided by one-third of the total eye height equation (1) [9]. As a result, PAM-4 necessitates sophisticated equalization techniques and strong error correction methods to guarantee reliable transmission over extended distances.

Figure 6: PAM4 transmitter output levels and linearity definition

$$RLM = \frac{\min(A,B,C)}{(A+B+C)/3} \tag{1}$$

In summary, both NRZ and PAM-4 serve as vital methods for encoding binary data in digital communication systems, each with its unique advantages and limitations. The choice between these encoding schemes is influenced by factors such as data rate requirements, bandwidth availability, and the overall complexity of the communication infrastructure, highlighting the importance of understanding their characteristics in the design of efficient digital networks.

### 4 State-of-the-Arts VM transmitters

In recent years, VM transmitters have seen substantial advancements, primarily driven by the escalating demands for high-speed data transmission in today's communication systems. As data rates continue to soar, it has become increasingly essential for drivers to not only handle these elevated speeds but also to improve power efficiency and maintain signal integrity. This evolution is vital, as it has a direct impact on the performance and reliability of high- speed digital interfaces, which are critical for applications ranging from telecommunications to data centers. In this context, understanding the underlying mechanisms and components of VM transmitters is key to addressing these challenges. This section offers a comprehensive literature review focusing on the primary functional building blocks of VM transmitters, examining their roles, advancements, and contributions to enhancing overall system performance.

#### 4.1 Serialization

A serializer is an essential component that transforms parallel input words into serial data, facilitating high-speed data transmission. The delay difference between the clock path and the data path at each stage of the serializer can have a considerable effect on performance. This delay difference is affected by variation in the process, supply voltage, and temperature (PVT), which can increase jitter in the data eye and degrade the performance of the interface. Moreover, a delay difference greater than 1 unit interval (UI) may lead to setup and hold violations [31]. A commonly adopted and effective solution to address this challenge is the insertion of replica clock buffers in the clock path. One of the most widely used architectures is the binary tree serializer, which operates as a  $2^N$ : 1 multiplexer made up of series 2:1 multiplexers. This design is particularly power-efficient in its initial stages, where static CMOS flip-flops and multiplexers can be employed due to the lower data rates. Also, the binary tree architecture can operate at halfrate to save power, but this will be sensitive to any duty-cycle distortion. In [32, 33], the binary tree architecture was operating at full-rate. In [34, 35], the binary tree architecture was operating at half-rate. This architecture becomes power hungry and sensitive to any process, supply voltage, and temperature variation if the serializer is multi-stage. Also, another disadvantage of it is the difficulty in implementing this architecture in the case of input data other than  $2^N$ : 1 such as 10b or 20b input data. Another architecture commonly used for the implementation of any number of input parallel bits is the shift register as in [10, 31].

### 4.2 Driver

VM drivers are essential components in high-speed serial communication systems, where rapid and reliable data trans- mission is of utmost importance. These drivers function by converting digital signals into appropriate voltage levels that can effectively drive the transmission line, thereby ensuring that data integrity is preserved over extended distances and across various transmission media. However, power consumption remains a critical factor in the design, as excessive power usage can become a significant bottleneck. Research has shown that current-mode (CM) drivers can consume up to four times the power of their voltage-mode (VM) counterparts [36–39].

Among the various configurations, source series terminated (SST) drivers are the most prevalent topology used in VM drivers [10, 33, 40–42]. In this configuration, a resistor is placed in series with the output, effectively matching the driver's impedance to that of the transmission line, as illustrated in <u>Fig.4b</u>. This approach offers dual benefits: first, it divides the termination resistance between the transistor and the series resistor, thereby improving impedance matching most designs typically employ a larger resistor compared to the inherent resistance of the transistor. Second, the configuration drives the transistor into deep-triode operation, where its resistance is primarily controlled by the gate voltage. This effectively decouples the termination from the voltage swing, allowing for a more stable performance.

By ensuring a proper impedance match, the SST driver can generate a robust voltage swing while minimizing signal distortion. This makes them particularly suitable for high-speed applications such as PCIe, SATA, and Ethernet, where maintaining high data rates is critical. Furthermore, SST drivers can integrate advanced features like pre-emphasis and equalization, which help to combat inter-symbol interference and other channel impairments. This combination of performance enhancements and design simplicity makes SST drivers an attractive choice for modern communication systems, balancing the need for efficiency with the demands of high-speed data transmission.

In summary, as the demand for faster and more reliable data transmission continues to grow, VM drivers, particularly those utilizing SST configurations, will remain at the forefront of innovation in high-speed communication technologies. Their ability to maintain signal integrity while minimizing power consumption positions them as vital components in the evolving landscape of data communication.

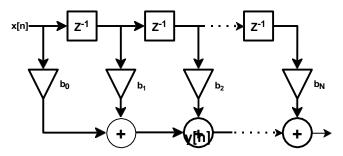

### 4.3 Equalization

Feedforward Equalization (FFE) is a type of equalization that compensates for the signal degradation by amplifying or attenuating specific frequency components of the signal. FFE is implemented using a linear filter, which boosts or attenuates the high-frequency components of the signal. It consists of several taps, each representing a coefficient that processes the input signal as shown in Fig.7. The FFE circuit uses an equalizer tap to adjust the filter coefficients. The number of taps determines the filter's complexity and its ability to compensate for the channel impairments. FFE can compensate for channel impairments such as attenuation, dispersion, and crosstalk. However, FFE is not effective in mitigating inter-symbol interference (ISI). The filter operates by attenuating low-frequency content when a stream of 1's or 0's is present, while allowing full signal swing during data transitions, effectively creating a high-pass filtering effect to counteract channel low-pass filtering. Common voltage mode equalization techniques include segmenting the driver into parts assigned to main, post, or pre cursors with inverted polarity, or using binary weighted slices for better decoupling. However, these methods tend to incur a highpower penalty due to opposing current flow needed for signal attenuation. To mitigate power penalties, several solutions have been proposed, such as adding a shunt network to stabilize current regardless of equalization settings as in [10, 28] or implementing a half-rate decoder to further reduce power consumption as in [43]. These designs may still face challenges like degraded return loss, which could affect signal integrity, especially in industrial applications that require compliance with standards.

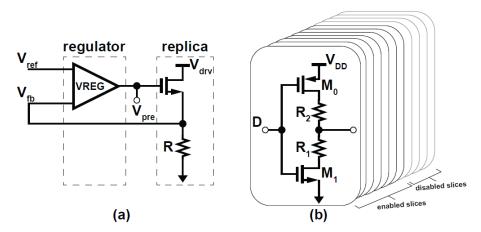

### 4.4 Impedance Matching

The primary challenge of VM drivers is managing the termination in relation to the voltage swing. As the voltage levels change, it is crucial to keep the termination impedance properly matched to maintain signal integrity. Fluctuations in swing can result in reflections and distortions if the termination isn't adjusted accordingly, potentially degrading the performance of high-speed digital

Figure 7: Block diagram of a 'N' order FIR filter

Communication systems In [40], a straightforward method for controlling the output impedance of a high-swing VM driver is to incorporate redundant segments that can be digitally activated to align with the channel impedance. In [10], a regulator was used to control the supply of the pre-driver in order to achieve the appropriate termination resistance.

Figure 8: Impedance calibration using (a) analog calibration and (b) digital calibration

### **5 LIMITATIONS**

VM drivers in high-speed data transmission face several critical limitations despite their technological advancements. While generally more power-efficient than CM alternatives, their power consumption increases significantly when implementing advanced features like preemphasis and PAM-4 signaling, which require additional circuitry for managing multiple signal levels and maintaining signal integrity. Signal integrity poses another major challenge, particularly at higher data rates where noise susceptibility increases and signal-to-noise ratio (SNR) may be compromised, especially with PAM-4's reduced eye height. The complexity of designing these drivers is compounded by the need for precise impedance matching, output swing regulation, and integration of sophisticated features like dynamic load control and impedance modulation, all of which must work harmoniously to maintain optimal performance across varying operating conditions. Additionally, the limited flexibility in adapting to various communication standards

presents a significant hurdle, as the inherent trade-offs between performance, power efficiency, and complexity can restrict their applicability in multi-standard applications, where adaptability is essential for meeting diverse communication requirements. These challenges collectively highlight the ongoing need for innovative solutions that can enhance VM driver performance while addressing these fundamental limitations in high-speed communication systems.

Table 1 illustrates a comparison between different VM drivers.

**Table 1:** Comparison between techniques

| Parameter        | [10]   | [33]   | [28]  | [40]  | [39]  | [42]   |

|------------------|--------|--------|-------|-------|-------|--------|

| CMOS Technology  | 65nm   | 28-nm  | 65-nm | 65-nm | 12-nm | 28-nm  |

| Туре             | NRZ    | hybrid | NRZ   | PAM-4 | PAM-4 | hybrid |

| Supply (V)       | 1.2    | 1      | 1.2   | 1.2   | 1     | 1      |

| Swing (Vpp)      | 0.3-1  | 0.5    | 0.2   | 0.5   | 0.8   | -      |

| Power (mW)       | 5      | 5.5    | 10    | -     | 48.5  | 72.96  |

| Data rate (Gb/s) | 1.5-12 | 21     | 10    | 18    | 50    | 48     |

#### 6 CONCLUSION

This article provides a comprehensive review of VM drivers for serial-link applications, highlighting their growing preference over CM drivers due to lower power consumption, despite challenges in output swing management and impedance matching. It explores the two main VM driver configurations (N-over-N and P-over-N) and compares the traditional NRZ signaling with PAM-4, noting that while PAM-4 offers double the data rate, it faces significant challenges in signal integrity with its reduced eye height. The review demonstrates that despite significant advances in VM driver technology, several key challenges persist, including increased power consumption when implementing advanced features like pre-emphasis and PAM-4 signaling, signal integrity issues at higher data rates, complex design requirements for impedance matching and output swing regulation, and limited flexibility in adapting to various communication standards, all of which impact their performance and applicability in modern high-speed communication systems.

### References

- 1. El-Sayed, H.M.Y.; Hasaneen, A.M. Plv/pac feature extraction units for implantable neural interfaces: Review. Aswan Univ. J. Sci. Technol. 2024, 4, 72–79.

- 2. Yokoyama-Martin, D.A.; Krishna, K.; Stonick, J.; Caffee, A.; Gamble, E.K.; Jones, C.; McNeal, J.; Parker, J.; Segelken, R.; Sonntag, J.; Umino, K.; Upton, J.; Weinlader, D.; Wolfer, S. A multi-standard low power 1.5–3.125 Gb/s serial transceiver in 90nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2006, 53, 401–404.

- 3. Hollis, T.M.; Schneider, R.; Brox, M.; Hein, T.; Spirkl, W.; Bach, M.; Balakrishnan, M.; Dietrich, S.; Funfrock, F.; Ivanov, M.; Jovanovic, N.; Kuzmenka, M.; Lauber, D.; Ocon-Garrido, J.; Ovard, D.; Pfefferl, K.; Piatkowski, S.; Piscopo, G.; Plan, M.; Polney, J.; Pottgiesser, J.; Rau, S.; Vitale, F.; Walter, M.; Alvarez-Gonzalez, M.; Broschwitz, M.; Chetreanu, C.; Sorrentino, A.; Weller, J.; Mayer, P.; Richter, M.; Garcia, C.S.; Schneider, A.; Wong, S.N. 25.3 An 8Gb GDDR6X DRAM achieving 22Gb/s/pin with single-ended PAM4 signaling. IEEE J. Solid-State Circuits 2021, 56, 348–350.

- 4. Yang, N.H.-W.; Roshan-Zamir, A.; Song, Y.-H.; Palermo, S.M. A low-power dual-mode 20-Gb/s NRZ and 28-Gb/s PAM-4 voltage-mode transmitter. In Proceedings of the 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), Jeju, Korea, 6–8 November 2017; pp. 261–264.

- 5. Jeong, Y.-U.; Park, H.; Hyun, C.; Chae, J.-H.; Jeong, S.-H.; Kim, S. A 0.64-pJ/bit 28-Gb/s/pin high-linearity single-ended PAM-4 transmitter with an impedance-matched driver and three-point ZQ calibration for memory interface. IEEE J. Solid-State Circuits 2021, 56, 1278–1287.

- 6. Hyun, C.; Jeong, Y.-U.; Kim, S.; Chae, J.-H. An 18-Gb/s/pin single-ended PAM-4 transmitter for memory interfaces with adaptive impedance matching and output level compensation. Electronics 2021, 10, 1768. Available online: https://doi.org/10.3390/electronics10151768 (accessed on 8 June 2025).

- 7. Zheng, X.; Zhang, C.; Lv, F.; Zhao, F.; Yue, S.; Wang, Z.; Li, F.; Jiang, H.; Wang, Z. A 4–40 Gb/s PAM4 transmitter with output linearity optimization in 65 nm CMOS. In Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 23–26 April 2017; pp. 1–4. Available online: https://api.semanticscholar.org/CorpusID:23380290 (accessed on 8 June 2025).

- 8. Dikhaminjia, N.; He, J.; Hernandez, E.; Tsiklauri, M.; Drewniak, J.L.; Chada, A.; Zvonkin, M.; Mutnury, B. High-speed serial link challenges using multi-level signaling. In Proceedings of the 2016 IEEE Electrical Design of Advanced Packaging and Systems (EDAPS), Singapore, 5–7 December 2016; pp. 57–60. Available online: https://api.semanticscholar.org/CorpusID:47450401 (accessed on 8 June 2025).

- 9. Razavi, B. Design techniques for high-speed wireline transmitters. IEEE Open J. Solid-State Circuits Soc. 2021, 1, 53–66.

- 10. Megahed, M.; Rizk, M.R.M.; Ibrahim, S.A.; Dessouky, M. 12-Gb/s low-power voltage-mode driver for multi-standard serial-link applications. In Proceedings of the 2016 IEEE Electrical Design of Advanced Packaging and Systems (EDAPS), Singapore, 5–7 December 2016; pp. 101–104.

- 11. Chan, K.L.; Tan, K.H.; Frans, Y.; Im, J.; Upadhyaya, P.; Lim, S.W.; Roldan, A.; Narang, N.; Koay, C.Y.; Zhao, H.; Chiang, P.-C.; Chang, K. A 32.75-Gb/s voltage-mode transmitter with three-tap FFE in 16-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 2663–2678.

- 12. Meghelli, M.; Rylov, S.; Bulzacchelli, J.; Rhee, W.; Rylyakov, A.; Ainspan, H.; Parker, B.; Beakes, M.; Chung, A.; Beukema, T.; Peppeljugoski, P.; Shan, L.; Kwark, Y.; Gowda, S.; Friedman, D. A 10Gb/s 5-tap-DFE/4-tap-FFE transceiver in 90nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2006, 53, 213–222.

- 13. Beukema, T.; Sorna, M.; Selander, K.; Zier, S.; Ji, B.; Murfet, P.; Mason, J.; Rhee, W.; Ainspan, H.; Parker, B.; Beakes, M. A 6.4-Gb/s CMOS SerDes core with feed-forward and decision-feedback equalization. IEEE J. Solid-State Circuits 2005, 40, 2633–2645.

- 14. Rao, V.S.P.; Mandal, P. A new power efficient current-mode 4-PAM transmitter interface for off-chip interconnect. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 959–962.

- 15. Gu, Y.; Chen, J.; Li, X.; Chen, Y.; Wu, J. A 32Gb/s NRZ wireline transmitter with CMFB-based CML driver in 28nm CMOS technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 14–17.

- 16. Seong, K.; Lee, W.-C.; Kim, B.; Sim, J.-Y.; Park, H.-J. All-synthesizable current-mode transmitter driver for USB2.0 interface. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 788–792.

- 17. Lv, F.; Zheng, X.; Yuan, S.; Wang, Z.; He, Y.; Zhang, C.; Wang, Z.; Lv, F.; Wang, J. A 40–80 Gb/s PAM4 wireline transmitter in 65nm CMOS technology. In Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 23–26 April 2017; pp. 539–542.

- 18. Chien, M.-H.; Lee, Y.-L.; Goh, J.-R.; Chang, S.-J. A low power duobinary voltage mode transmitter. In Proceedings of the 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), Jeju, Korea, 6–8 November 2017; pp. 1–6.

- 19. Dettloff, W.D.; Eble, J.C.; Luo, L.; Kumar, P.; Heaton, F.; Stone, T.; Daly, B. A 32mW 7.4Gb/s protocolagile source-series-terminated transmitter in 45nm CMOS SOI. In Proceedings of the 2010 IEEE Electrical Design of Advanced Packaging and Systems (EDAPS), Singapore, 5–7 December 2010; pp. 370–371.

- 20. Menolfi, C.; Hertle, J.; Toifl, T.; Morf, T.; Gardellini, D.; Braendli, M.; Buchmann, P.; Kossel, M. A 28Gb/s source-series terminated TX in 32nm CMOS SOI. In Proceedings of the 2012 IEEE Electrical Design of Advanced Packaging and Systems (EDAPS), Singapore, 5–7 December 2012; pp. 334–336.

- 21. Menolfi, C.; Toifl, T.; Rueegg, M.; Braendli, M.; Buchmann, P.; Kossel, M.; Morf, T. A 14 Gb/s high-swing thin-oxide device SST TX in 45 nm CMOS SOI. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2011; pp. 156–158.

- 22. Bandarupalli, J. D.; Gautam, R.; Saxena, S. A reconfigurable 0.1–10 Gb/s voltage-mode transmitter with 0.2–1 V output swing. IEEE Solid-State Circuits Lett. 2019, 2, 53–56.

- 23. Kim, J.; Balankutty, A.; Elshazly, A.; Huang, Y.-Y.; Song, H.; Yu, K.; O'Mahony, F. 3.5 A 16-to-40 Gb/s quarter-rate NRZ/PAM4 dual-mode transmitter in 14 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2015; pp. 1–3.

- 24. Peng, P.-J.; Chen, Y.-T.; Chen, C.-H.; Lai, S.-T.; Huang, H.-E.; Lu, H.-H.; Yu, T.-C. A 50 Gb/s quarter-rate voltage-mode transmitter with three-tap FFE in 40-nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2018; pp. 174–177.

- 25. Kim, S.; Jeong, Y.; Lee, M.; Kwon, K.-W.; Chun, J.-H. A 5.2 Gb/s low-swing voltage-mode transmitter with an AC-/DC-coupled equalizer and a voltage offset generator. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 213–225.

- 26. Chiou, H.-K.; Sung, W.-M. A 5 to 10.5 GHz low-power wideband I/Q transmitter with integrated current-mode logic frequency divider. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2019; pp. 1–4.

- 27. Li, M.; Yuan, F. A new fully differential 4-PAM current-mode transmitter for 10 Gbps serial links in 0.13 μm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2005; Volume 2, pp. 1665–1668.

- 28. Lu, Y.; Jung, K.; Hidaka, Y.; Alon, E. Design and analysis of energy-efficient reconfigurable pre-emphasis voltage-mode transmitters. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 48, 1898–1909.

- 29. Peng, P.-J.; Lai, S.-T.; Wang, W.-H.; Lin, C.-W.; Huang, W.-C.; Shih, T. A 100 Gb/s NRZ transmitter with 8-tap FFE using a 7b DAC in 40 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2020; pp. 130–132.

- 30. Frans, Y.; McLeod, S.; Hedayati, H.; Elzeftawi, M.; Namkoong, J.; Lin, W.; Im, J.; Upadhyaya, P.; Chang, K. A 40-to-64 Gb/s NRZ transmitter with supply-regulated front-end in 16 nm FinFET. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2016; pp. 68–70.

- 31. Jeong, Y.-U.; Chae, J.-H.; Choi, S.; Yun, J.; Jeong, S.-H.; Kim, S. A low-power and low-noise 20:1 serializer with two calibration loops in 55-nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2019; pp. 1–6.

- 32. Cao, J.; Green, M.; Momtaz, A.; Vakilian, K.; Chung, D.; Jen, K.-C.; Caresosa, M.; Wang, X.; Tan, W.-G.; Cai, Y.; Fujimori, L.; Hairapetian, A. OC-192 transmitter and receiver in standard 0.18 μm CMOS. IEEE J. Solid-State Circuits 2002, 37, 1768–1780.

- 33. Kim, S.-H.; Kim, S.-H.; Jin, X.; Lee, Y.; Chun, J.-H. A 21 Gb/s dual-channel voltage-mode transmitter with stacked NRZ and PAM4 drivers. IEEE Access 2018, 6, 1. Available online: https://ieeexplore.ieee.org/document/8485682/metrics#metrics (accessed on 8 June 2025).

- 34. Bulzacchelli, J.; Meghelli, M.; Rylov, S.; Rhee, W.; Rylyakov, A.; Ainspan, H.; Parker, B.; Beakes, M.; Chung, A.; Beukema, T.; Pepeljugoski, P.; Shan, L.; Kwark, Y.; Gowda, S.; Friedman, D. A 10 Gb/s 5-tap DFE/4-tap FFE transceiver in 90-nm CMOS technology. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2006; Volume 41, pp. 213–222. Available online: https://ieeexplore.ieee.org/document/1696051 (accessed on 8 June 2025).

- 35. Menolfi, C.; Toifl, T.; Buchmann, P.; Kossel, M.; Morf, T.; Weiss, J.; Schmatz, M. A 16 Gb/s source-series terminated transmitter in 65 nm CMOS SOI. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2007; pp. 446–614.

- 36. Choi, E.-J.; Kim, S.; Jeong, Y.-K.; Kwon, K.-W.; Chun, J.-H. A low-swing AC- and DC-coupled voltage-mode driver with pre-emphasis. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2011; pp. 1–4.

- 37. Lee, S.-K.; Kim, B.; Park, H.-J.; Sim, J.-Y. A QDR-based 6-Gb/s parallel transceiver with current-regulated voltage-mode output driver and byte CDR for memory interface. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 91–95. https://doi.org/10.1109/TCSII.2012.2225635

- 38. Saxena, S.; Nandwana, R.K.; Hanumolu, P.K. A 5 Gb/s energy-efficient voltage-mode transmitter using time-based de-emphasis. IEEE J. Solid-State Circuits 2014, 49, 1827–1836. https://doi.org/10.1109/JSSC.2014.2326155

- 39. Kashani, M.H.; Shakiba, H.; Sheikholeslami, A. A low-power high-BW PAM4 VCSEL driver with three-tap FFE in 12-nm CMOS FinFET process. IEEE J. Solid-State Circuits 2024, 59, 1995–2004. https://doi.org/10.1109/JSSC.2024.3365678

- 40. Kim, S.-H.; Cho, B.; Jin, J.; Song, Y.H.; Chun, J.-H. A 16/32 Gb/s dual-mode NRZ/PAM4 voltage-mode transmitter with 2-tap FFE. IEEE Access 2022, 10, 119140–119149. https://doi.org/10.1109/ACCESS.2022.3226789

- 41. Wang, X.; Gui, P. A hybrid transmitter with voltage-mode SST preemphasis and current-mode transmitter equalization capable of operating at 77 K in DUNE. IEEE Trans. Nucl. Sci. 2023, 70, 262–271. https://doi.org/10.1109/TNS.2023.3242246

- 42. Zhou, J.; Jin, J.; Lin, Y.; Wang, S.; Wang, B.; Mo, T. A 24/48 Gb/s NRZ/PAM-4 dual-mode transmitter with 3-tap FFE in 28 nm CMOS. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 2023; pp. 1–4.

- 43. Kocaman, N.; Ali, T.; Rao, L.; Singh, U.; Abdul-Latif, M.; Liu, Y.; Hafez, A.; Park, H.; Vasani, A.; Huang, Z.; Iyer, A.; Zhang, B.; Momtaz, A. A 3.8 mW/Gbps quad-channel 8.5–13 Gb/s serial link with a 5-tap DFE and a 4-tap transmit FFE in 28 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 1–12. https://doi.org/10.1109/JSSC.2015.2502619